并行同步计算机,一般指的是在同时实行两个或多个资料库、档案、模组、执行绪之间用来保持数据内容一致性的机制的一种由于高速计算的电子计算机器。

基本介绍

- 中文名:并行同步计算机

- 外文名:parallel synchronous computer

- 分类:计算机

用软体实现并行计算机系统的时钟同步

提出了利用软体同步实现TANSPUTER系统中各处理器时钟同步方法。首先对并行计算机系统的时钟同步问题进行了介绍;然后对一种多处理器的同步算法简单地进行了描述,并给出了在990一 STAR并行计算机系统中实现的方法;提供了部分程式代码和注解以及在990一STAR并行计算机系统中获取的结果;讨论了代码的实用性和可移植性。

同步问题

系统就被认为同步,这可以通过相应的硬体和软体技术来实现。 讨论非容错的软体同步方法,其同步思想就是通过并行计算机系统中节点网际网路中的信息交换来计算同步硬体时钟时所需的调整值。具体实现过程就是假定处理节点中某个处理器的时钟作为参考时钟(主时钟),然后使并行计算机系统中其它的时钟值与其保持一致,这种机制可通过周期地广播主时间、并设定从时钟的值与它接收到的时间值相等来实现。

在系统软体设计时,因为时间管理总是属于最高优先权别的进程,系统总是会立即回响时间管理进程,这样不管Sender和Receiver进程谁先激活,其间的延迟可以用一些常数单位rdmin(最小激活延迟单位)来度量,虽然不知準确的激活延迟为多少,但可以通过将首先激活的进程人为延迟rdmin来得到部分补偿。

算法实现和程式结构

算法利用并行C语言和TRANSPUTER彙编语言混合编写、并已在研製的990一STAR并行计算机系统上侧试通过,990一STAR为鬆散藕合的并行计算机系统,包括16个数据处理节点和一个专用图像处理节点,每个数据处理节点由TRANSPUTER T805和Intel i860通过存贮共享藕合而成,每个i86。具有强大的计算能力,主要完成大负荷的计算。各节点之间的通讯通过T805及其通讯链来实现。为了便于系统的扩展和降低硬体的複杂性,整个系统没有设定硬体全局时钟,各节点之间的同步採用软体时钟来实现。 在TRANSPUTER系统中,LINK不能为几个同时被激活的进程共享,所以通信不会因LINK的吞吐量而受影响,对于进程激活延迟只要在首先激活的进程中加入适当的记rdmin即可,因为对于以LINK直接连线的节点,数据交换时,总是sender先于Rceciver结束,而对于以C004相连线的节点,情况就不一样。总之,通过在Master或Slaver同步代码中插入适当的延时就能补偿激活延迟误差。

程式的核心部分为相邻PE之间同步延迟的估算,这部分任务由进程send_time和receive_time来完成,receive_time进程还需进行漂移误差补偿,然后设定时钟值,在这两进程中还要考虑由于激活顺序差异而需补偿的时延值rdmin,rdmin加在哪一进程中完全视硬体连线方式而定。

程式基本结构的进程slaver被放在每一个从节点上,进程master放在主节点上,master进程控制广播时钟的间隔时间并广播时钟,slaver进程负责从选中的通路中接收时钟值,这步工作通过调用receive_time进程完成,并向指定的连线通路中传播时钟值,这步工作通过send_time进程来完成,进程slaver中BOOL变数sync_flag用来标明接收通路和传送通路,其值由link_inPut过程来完成设定,BOOL型函式sel_sync用来确定与某PE相连的LINK中哪些可用来作同步信号的传输。master进程的结构与lslaver进程非常相似,只是不用接收外部的时钟信号。

运行试验结果

在990一STAR并行计算机系统上进行了程式调试和运行试验,990一STAR并行机系统由基于TRANSPUTER通信的17个节点(PE)构成,所以只能获得d<≈16的试验结果。在试验中发现eδ≤1μs,也就是说相邻两节点间初始同步误差在1滴哒内(tick),这样争对假设漂移误差和同步激活最大误差中的初始同步误差上限在dμs内,实际的ei0远比它的上限小,对d ~16的情况做了1000次试验,其分布情况对16个从PE上作四轮同步操作,每一轮间隙10s所得的最大漂移误差的分布情况,这些表明採用线性漂移补偿导致的漂移误差eid(t)可以忽略。 ei的一组典型值显示了总的同步误差情况,可以看到在d一61的系统中误差範围在0一3μs之间。由程式结构可知 , ,在每一轮同步过程中,相邻节点间的通信量为(21)Byte同步信号和4Byte的时钟值,通信开销和用户程式所需的通信量相比可以忽略,採用这种方法同步时通信所占的系统开销量极小。

容错机制的并行计算机系统中同步策略

针对基于容错的并行计算机系统的高可靠性和高效性的要求,探讨了多机系统中较难解决的同步策略。从系统上电同步、任务调度同步和表决同步三个方面提出了容错与并行处理系统的同步方案,并在样机上实现。

系统结构

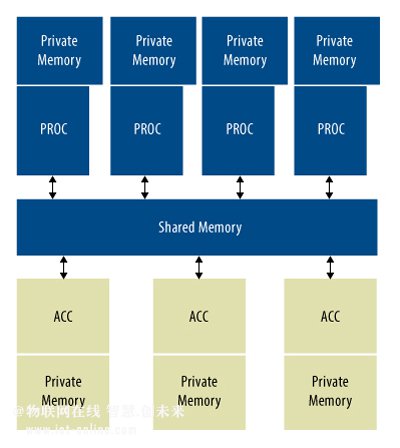

系统採用三模冗余结构,每个模组主要由计算机、存储器和汇流排接口单元BIU(Bus Interface Unit)构成。模组内部的存储器仅供模组中的计算机使用,SM为系统共享存储器,它供整个系统存放信息及其表格参数,整个系统构成了一个紧藕合的多机系统。汇流排接口单元BIU是模组与系统汇流排之间的瓶颈,每个模组都是通过BIU挂接于汇流排。BIU具有离汇流排与模组的作用,由于三个模组共用一条汇流排,在某一时刻只能有一个模组使用汇流排,通过BIU的内部机制,可以完成模组对汇流排的打开与封锁,对数据进出汇流排起到控制作用,从而隔离模组与汇流排。另外通过BIU还可以将故障的模组隔离,进行系统重构。系统设计的另一特色是採用了并行汇流排(BUS)和串列汇流排(SBUS)兼有的双汇流排结构。SBUS连线各CPU的串口,并行汇流排具有汇流排控制(BC)权模组,且持有令牌,令牌在各模组之间的传递是通过SBUS完成 。

系统软体

系统主要是由软体实现容错和并行调度管理。系统软体是一个多机容错与并行处理的作业系统 , 它负责系统的任务调度、通信机制、同步机制与执行过程的控制和管理。在同步策略模组中实现三模表决与并行处理以及发生故障时的降级重构。系统的同步策略、冗余管理与并行调度是系统的核心工作。

同步策略

对于多机系统同步是必须要解决的问题,同步策略的优劣直接关係到整个系统多机之间的协调工作、资源分配才不会产生冲突。根据系统的自身特点,把同步策略分为系统上电同步、任务调度同步和表决同步三个方面来考虑。

1、上电同步策略:在常规的多机系统中,每个模组都加入一个时钟电路。虽然模组内部能做到同步,但在各模组间时钟误差累积到一定程度后,就会使系统处于崩溃。系统中只採用一个时钟电路,这样系统一开机上电便处于同步状态。开机上电后各模组开始进行各自的初始化。A模组首先具有BC汇流排控制权,它向其它两模组发同步信号,然后三个模组根据任务调度算法调度相同的任务进行容错处理,系统便开始处于任务级同步。

2、任务调度而产生的同步策略:在进行任务划分时,根据所完成任务的特点和解决方法,将它们事先做容错和并行划分,使系统在运行过程中被合理地调度。当从容错状态切换到并行工作状态时,不需要多机之间的协调,各机可直接调用并行处理任务。

从并行到容错状态切换採用等待完成调度算法(即先完成的处理机等待其它处理机完成并行任务,然后再调度一个任务进行多机仿作), 具体同步处理过程描述算法如下:

void synchroni Zation(void){

while(本机工作正常){

if(有工作尚未完成){

继续处理本机工作;}

else{

向其它模组发完成信号;};

if(本机具有BC权){

if(有模组提出升级申请){

调用测试程式检查其正确性;

if(模组正确)

系统升级;

}

do{waiting;}

until(其它模组的完成信号到);

if(上一任务为并行处理任务){

根据任务调度算法选择一容错任务;

向其它模组发容错处理信号并将任务号一起传出);

执行这个任务进行容错处理}。

else{向其它模组发并行处理信号;

根据任务调度算法选择一併行任务;

执行这个任务;

}

else{

do{waiting;}

until(具有BC权的模组发来下一步处理信号);

if(下一步为容错处理){

提取该任务号;

调度并执行该任务;

}

eles{根据任务调度算法选择一任务;

执行该任务;

};

};/*while*/

}

3、同步表决策略:同其它的容错计算机系统一样,在完成容错任务后要对三机运行结果进行大数表决,以此来减小系统运行出错的机率,提高系统的可靠性。在每次表决之前,先完成的模组要等待后完成的模组,这在一定程度上可减小模组间的异步。系统的同步表决策略与其余的容错计算机系统基本相同,但是 ,由于它是一套特殊的容错系统,在运行的过程中混有并行处理机制,因此在出错误后的解决方案就截然不同。